Intel众核处理器战略解析与技术前瞻

或许您已经用上了8核手机,或许Ivy Bridge-E甚至双路12核心服务器已成为您的办公用机,或许您认为处理器的核心数目已经多得完全用不上。别担心,处理器的多核心革命只是刚刚开始。目前,一款核心数多达72核心的英特尔处理器已经初具雏形,在不远的将来就会投入使用。那么它为什么需要这么多核心?哪一款软件会用到如此多的核心?这种新的处理器又将主要用于哪些领域?本文将为读者朋友们一探究竟。

源于GPGPU与异构计算的威胁

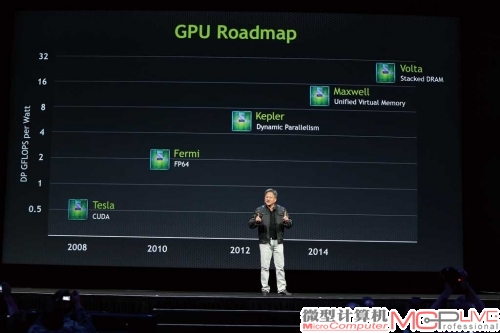

发展核心数如此之多的一款处理器,当然不是因为现今处理器已无法满足普通消费者的需求,而是在于英特尔感受到GPGPU架构与异构计算对自己在高性能运算领域造成了切实的威胁。从上世纪九十年代开始计算,GPU与CPU已在长达十余年的时间里一直各司其职,保持着井水不犯河水的状态,但快速发展的半导体行业不会甘于持久的平静。CPU单核性能的提高受到功耗、访存速度、设计复杂度等多重瓶颈的制约,逐渐显露颓势。据美国国防部高级研究计划局罗伯特·科威尔在Hotchips 2013大会上给出的新评估,此后的CPU每次换代只能提升多10%左右的性能,随着线宽逐渐缩减,就连维持这一进步幅度都会变得越来越困难。而追求吞吐量的GPU受到摩尔定律的护佑,在过去这些年中得以不断地在有限的芯片面积内塞入越来越多的简单核心。其暴力计算速度开始展现锋芒,加上科学计算、多媒体处理等等具备较好并行性的领域需求推动,GPU开始不甘于“寄人篱下”,尝试提高自身的可编程性,“接管”一部分适合自己进行运算的应用。

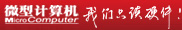

大力推广CUDAGPU的英伟达,如今已经成为GPGPU浪潮中的大赢家。

所谓提高可编程性,就好比令一把只能砍树的斧头,变身成为能够应对多种用途的瑞士军刀,这种“瑞士军刀”式的GPU被称为GPGPU。CPU单线程性能的增长潜力已经越来越难发掘,当工业界和学术界都开始寻找其他的性能增长点时,目光自然落到了GPGPU身上。自从英伟达开始发力推广GPGPU概念以来,GPU的专长便开始逐渐深入人心。越来越多的架构师开始重新审视GPU在整个计算机系统中的地位,在系统架构设计时对GPU的作用加以考虑。程序员们也开始尝试将合适的代码转移到GPU上执行。为了配合GPU的并行特征,从代码中抽取并行性,CUDA、Open CL等新的编程语言、框架、模型相继提出,这个过程成为了底层体系结构影响上层编程语言的典型范例。

GPGPU的成功,在高性能计算市场上得到了非常明显的体现。进入2010年以后,采用GPGPU的超级计算机数目迎来了堪称爆发的高速增长,超级计算机五百强榜单中逾十分之一的机器选择了这种CPU-GPU异构的模式。在近年的GPGPU浪潮中,英伟达无疑成为大赢家。依据2012年中期的统计,采用GPU加速的超级计算机总数在60台上下,其中有50台左右采用了英伟达GPU。英伟达显然把握住了GPGPU这一浪潮,成为GPGPU在高性能计算中的领跑者。GPGPU的进化是如此的耀眼,甚至连普通用户都开始关心自己平常使用的软件是否具备GPU加速特性。GPU加速在浏览器、高清转码回放中的使用体验在各大论坛都可以见到讨论。从学术界、工业界到普通用户都已接受GPU在部分应用上具备独到优势的观点。部分受此因素的推进,新一轮异构计算的浪潮开始了酝酿,而这一轮大潮的推手已经不仅仅是NVIDIA,还包括AMD、ARM等等诸多宿敌与新锐。异构计算强调在系统中引入多个面向专门应用、关键应用的特殊处理单元。这些特殊处理单元的性能、功耗都胜过传统CPU,必要时可以接管对应的计算任务——显然,GPGPU将是这一系列五花八门的异构处理单元中耀眼的一个。GPU加速已经从初追求对性能优势的认可,逐渐发展为对计算理念进行整体革新的倡导者。而所有的这些,对坐惯了行业霸主地位的英特尔来说,都是危险的进犯信号。英特尔在CPU领域已经是事实上的寡头,计算理念这个大天平每次往异构和GPU那一侧倾斜一点儿,就意味着CPU的地位减弱一分,这无异于釜底抽薪,英特尔不可能束手旁观。

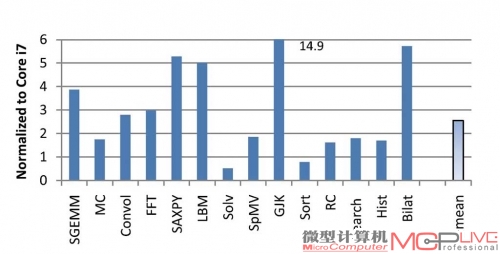

英特尔测试得出的GPU VS 多核CPU加速幅度,纵轴是GPU的相对性能倍数。

英特尔的反击——以众核收复失地

让我们换一个视角,来看看英特尔在超级计算机市场上的CPU占有率:在表现低落的2006年里,超级计算机五百强中仍有52%的系统使用英特尔的CPU。而此后七年,英特尔的占有率逐渐提高,2013年11月的新统计中已达82%,表面上看来形势一片大好,但GPGPU的兴风作浪令英特尔如鲠在喉。因为在这些超级计算机中,绝大多数的性能来自于GPGPU的贡献,大量的CPU几乎沦为陪衬。超级计算机是庞大IT产业中的璀璨明珠之一,甚至被作为一个国家科研实力的标志,围绕超级计算机的产品很容易诞生光环效应。而英伟达也很懂得新闻宣传中的四两拨千斤之道,往往抓住时机大肆渲染自己的GPU在超级计算机中如何占据主导地位,CPU与GPU之间又存在着怎样的性能与功耗鸿沟。面对这种情况,英特尔当然不会坐以待毙。巧合的是,当英伟达在高性能计算市场上凭借CUDA语言和Fermi GPGPU开始攻城略地之时,一篇来自英特尔吞吐计算实验室和体系结构组的学术论文出现在国际计算机体系结构大会(ISCA)上,论文标题是颇为轰动的《揭穿GPU百倍加速比神话》。

这篇论文选取了十四个已实现GPU加速的应用进行评估,结果显示,在双方都经过充分优化的情况下,GPU平均仅比多核CPU快了2.5倍,推翻了其他人声称可以实现数十倍、上百倍乃至上千倍加速比的先前研究结论。由于国际计算机体系结构大会是本领域内的旗舰级学术会议,审稿颇为严苛,声誉崇高,许多来自工业界的架构师和学术界的计算机科学家们都在关注这个会议的动向。因此这篇论文的出现毫不意外地引发轩然大波,一时间议论纷纷。这一结论有多少是出于学术目的,有多少是出于对多核CPU的商业利益保护,不得而知,但显然英特尔绝不会认同英伟达所走的GPGPU道路是计算机体系结构发展的未来所在。英特尔的芯片一向以卓越的性能表现著称,高性能计算市场上英特尔也实在当惯了寡头,这块大蛋糕是不会允许英伟达抢走的。为了匹敌英伟达的GPGPU战略,打破CPU核心不能实现高吞吐的论断,英特尔也开始酝酿自己的众核计划,并于2010年以前开始了工程样品Knights Ferry的研发,这个Knights Ferry后来演化成我们今天在市场上看到的Xeon Phi家族。

2012年,英特尔正式将第一代Xeon Phi产品,代号为Knights Corner的协处理器推向市场。这一代产品使用P54C核心构建,片上集成61个CPU核心,实现了GPU级别的浮点运算速度。但是,Knights Corner还不能称为完全的众核“处理器”,因为Knights Corner没有自己的CPU插槽,而是以类似显卡的方式,与GDDR5存储器一起做成一块板卡,插在PCI-E插槽上运行。因此,在宣传中经常将之称为众核协处理器或是加速卡。在推出一年后,异构超级计算机中采用英伟达GPGPU与采用英特尔众核协处理器的比例从53∶1变成了39∶11。在高性能异构计算市场的总体容量基本没有改变的情况下,英伟达的份额明显缩小,而英特尔的份额大幅增加。可以说Knights Corner在起步阶段已经做得相当不错,高性能异构计算已经不再是英伟达一家独大,而是越来越多地听到来自英特尔的声音。

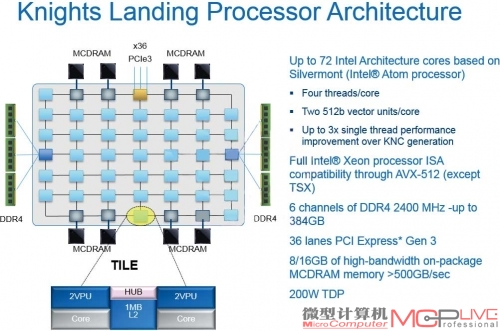

独立运行的72核心Knights Landing

随着越来越多的超级计算机开始尝试采用众核架构,天平重新向英特尔一侧倾斜,英特尔显然不愿意给对手太多机会。仅仅一年半后,英特尔就赶在新一届超级计算大会上公布了下一代产品Knights Landing的消息。面向超级计算机的Knights Landing将同时完成ticktock,也就是使用下一代14nm工艺制造的同时,也实现一次微架构的大幅度改进,将核心数目从61扩张到72,这样的消息不得不说是颇为令人心动的。依据眼下的情报,Knights Landing的变化主要可以归结为两大亮点:

在独立处理器与协处理器两种模式下运行

对于下一代众核架构的产品格局来说,可能这个变化是意义深远的。Knights Landing一举去掉了“协处理器”这个帽子,这款众核处理器可以继续在协处理器模式下运行,也可以作为独立处理器,整台超级计算机都使用Knights Landing来构建,不再需要Xeon的主导。依据目前英特尔放出的口风,新的独立CPU模式可能会摆脱PCI-E插槽,转而插在CPU插槽上,可独立启动自己的操作系统。使用协处理器模式的话,Knights Landing则仍然将工作在PCI-E插槽上,让已经部署了Knights Corner的机器能够快速升级。不过总体来看,以独立处理器模式工作时,Knights Landing的性能可以达到优化。毕竟在甩脱Xeon作为独立处理器之后,Knights Landing将解决数据在Xeon和Xeon Phi两种CPU之间迁移的问题。

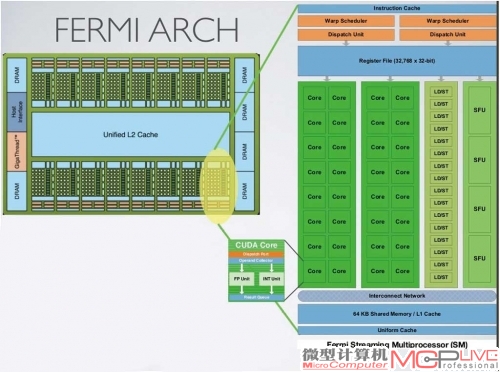

在超级计算机中,数据迁移的开销非常高昂。与普通民用领域不同,超级计算机上运行的代码里,仅仅一个数组的规模可能就达到TB级别,这样大规模的数据搬移到协处理器上所需要的延迟和功耗开销都不可忽视。性能调优时甚至需要考虑在搬移数据的同时进行计算,以求重叠数据搬移所浪费的时间。若Xeon Phi能够独立工作在可引导的独立处理器模式下,数据搬移的开销就可以免除,这是一项不小的优势。为了使更多的数据能够保存在本地,Knights Landing还在封装内部集成了一层内存,提供500GB/s的超高带宽以应对访存密集型的应用。

基础核心架构从P54C转向Silvermont

国外著名技术咨询站点Realworldtech曾于本次国际超级计算大会前刊登了一篇文章,预测Knights Landing的基础核心选择。该文认为Silvermont核心并没有像Haswell一样极致地追求单线程性能,而是走轻量级小核心的路线,核心设计时对单线程性能有所倚重,但并不激进,对注重多线程吞吐的Knights Landing来说可以接受,并且Silvermont自身已经是一个x86可引导核心,满足构建独立处理器的条件,因此可能会成为Knights Landing选择基础核心时的选项之一。但是若将这一架构搬迁至众核上,需要进行很大幅度的修改,绝非易事。Realworldtech据此认为,英特尔会选择再度重新出发,设计一个全新的核心。但是这一回,一向以内容专业、分析独到而著称的Realworldtech也犯错了。英特尔终选择了Silvermon,这是为什么?

第一:让Knights Landing作为独立处理器工作,虽然能应对数据迁移难题,但也同时意味着代码中的并行和串行部分都要搬移到Knights Landing上完成,如果仍旧坚持P54C,众核处理器将要以极度孱弱的单线程能力来应对x86-64代码中的串行部分。Silvermont的切入刚好使得单线程能力往前跃进了几乎一个时代,转向Silvermont的设计决策与独立CPU工作模式这二者是相辅相成的,可以说转向Silvermont就是Knights Landing引而不发的“独立宣言”。

第二:Realworldtech的分析没有错误,设计决策虽好,但是工程实现是另外一回事。在众核架构上引入Silvermont,从工程上来说确实有很多挑战。首先,为了适应高性能计算需求并且与前代产品保持一致,Silvermont需要引入至少512 bit位宽的SIMD阵列;为了具备多线程能力,流水线需要大幅翻新以控制多个执行线程。Silvermont的缓存系统对Knights Landing来说太过于寒酸,连Knights Corner都具备64字节/周期的读写带宽,但Silvermont只有区区16字节/周期。同时,Knights Corner的指令缓存是32KB 8路组关联,而Silvermont只有4路组关联,在多个线程代码争抢指令缓存时,恐将无法做到性能隔离。解决这些问题需要投入的工程努力是值得敬意的,很高兴看到英特尔的众核工程团队成功完成了一次跨越式进步。随着这一次改进,Knights Landing不仅能够维持x86前向兼容,还将自己的SIMD指令集也统一到AV X之上,英特尔此后的产品都将以AVX指令集作为SIMD扩展的基准。

外媒公布的Knights Landing PPT,显示这款下一代众核处理器将基于Silvermont架构构建

谁将成为后的赢家?多核 VS 众核 VS GPU

新一代众核处理器面世之后,高性能计算市场上将呈现一种非常有趣的三足鼎立格局:首先是来自英特尔的多核CPU,正在谋求扩张的英伟达GPGPU,以及奋起直追的众核CPU。这三者究竟是什么关系?

多核CPU与GPU是比较成熟的概念,让我们首先来对比一下英特尔所选择的的多核心CPU与英伟达的GPU路线有什么不同。CPU核心中普遍使用了激进的分支预测,乱序多发射技术,单线程的执行能力远远强于GPU,而GPU的单线程性能虽然低下,但是大规模并行架构造就了卓越的吞吐量。英特尔虽然在CPU领域具备统治力,但是架构的不同使得CPU无法在高吞吐的环境下与英伟达的GPGPU竞争,为后者留下可乘之机。

对于当下的GPGPU发展现状,业界大体存在两种观点,其一是保守派。他们认为GPGPU较难编程,且所有GPGPU代码本质上都能在CPU上运行。同时GPGPU的硬件架构与编程模型都在持续改进,今天花费很大力气调优的GPGPU加速代码,到了下一次产品更新时可能就已经丧失优势,GPGPU的高吞吐特性也只有面对一部分应用时才能发挥,所以GPGPU加速尚不急着上马。其二是乐观派,GPGPU在科学计算中非常活跃,其性能优势确实显著,花费额外精力进行GPGPU的调优是值得的。为了更好地配合GPGPU的硬件架构特点,甚至有一些领域的专用编程语言已被提出(例如专门用于计算化学问题)。显然乐观派对GPGPU的前途是相当看好的,这两种观点都有自身道理。

一头是在单线程性能上臻至巅峰,同时扩展少量核心提供少量并行性的多核CPU;另一头是在并行性上追求极致,但单线程性能上很差的GPGPU,这两者共同构成了现今的编程模型。而英特尔希望打破这一局面,利用一个新的架构,同时吸收多核CPU与GPGPU的长处,在CPU与GPGPU之间的空地上寻找立足点,这就是众核CPU。

回头分析众核CPU,我们能够从中找到一些明显属于GPGPU的特色。例如基于简单核心构建,以SIMD扩展为基本手段,强调吞吐量等等。同时也有不少来自CPU世界的理念,例如基于硬件管理的缓存一致性等。而众核CPU也吸收了多核CPU在编程方法上的长处,继承了OpenMP,MPI等编程语言,不会给程序员带来更大的代码迁移负担。OpenMP只需要给予相对简单的编译指导,程序代码就能实现半自动的并行化。其优点是开发难度小,缺点是编译器自动生成的并行代码不能完全发挥性能。而传统的GPGPU编程,如OpenCL和CUDA,都需要手动编写专用的并行代码,开发难度更高,但是性能表现通常较好。综上来看,众核CPU是定位在多核CPU与GPGPU之间的产物,吸收了多核CPU与GPGPU的长处,力图基于CPU核心提供大规模并行计算的能力。从目前的格局来看,从多核到众核到GPGPU,并行能力依次增强,串行能力则依次减弱,众核与多核CPU的市场重叠区间不算很大,但是与GPGPU却形成了正面交锋,形成针尖对麦芒的局势。这二者在未来几年内的竞争毫无疑问地将愈演愈烈。

采用14nm工艺生产,可独立运行的Knights Landing处理器势必和NVIDIA TESLA这类产品展开激烈角逐。

高性能大战才刚刚拉开序幕

随着Knights Landing的曝光,英特尔针对性地抛出了“ 同构计算”理念,认为众核CPU在未来有能力取代GPGPU,基于GPGPU的异构计算只不过是计算机体系结构发展中的一条分岔,主旋律终还会回到CPU核心上来。至此,英特尔已是“图穷匕见”,其众核架构战略蓝图已经有了比较明显的轮廓。下一代众核处理器Knights Landing将同时完成架构和工艺的双重进化,对于英伟达来说压力不可谓不大。针对英特尔的反击,英伟达也在做出调整,在近日公布的CUDA6中,无需程序员手动干预的自动化数据迁移也赫然在列。众核处理器与GPGPU的龙争虎斗现在才刚刚进入第二回合,孰胜孰负依旧难料。

Tips:什么是GPGPU的可编程性

GPGPU的底层架构与CPU有较大区别,这种架构的强大并行能力若想发挥出来,必须满足一些先决条件,让我们以SIMD处理为例来说明可编程性的概念。GPGPU的每一个核心实质上都是一个SIMD处理器,能够并行地计算几十组不相关数据的结果,但要求操作这几十组数据的指令都是相同的。若这些数据中的一半想做乘法,另一半想做除法,则在目前的架构中无法实现并行。GPGPU必须先发射一套乘法指令做完乘法运算,再发射一套除法指令去完成除法计算,这就对程序员们的编程提出了制约。程序员们必须将种类相同的计算尽可能地组合打包,才能发挥GPGPU的长处。相比之下CPU就没有这种限制,CPU能够同时发射多种类型的指令,这是GPGPU的可编程性不如CPU的原因之一。为了提高GPGPU的可编程性,包括CUDA,OpenCL在内的编程语言被相继提出,新的编程工具也在不断问世。

Tips:古老的P54C核心

P54C是一个完稿于1995年以前的老旧架构,距今已有近20年,P54C曾主要在Pentium 75到200处理器上得到广泛使用。选择它作为XeonPhi的主要原因在于其具备流水线短、核心简单的特性,具备较高的能耗效率,并通过后期改进,令其并行运算能力得到突破性提升,但其串行运算能力十分低下。

Tips:Xeon Phi的数据迁移

作为协处理器的Knights Corner,其运行模式与NVIDIA的GPGPU有类似之处。程序员都需要指定哪一部分代码在GPGPU/协处理器上运行,依据这个指示,相关的代码和数据将通过PCI-E总线传递至GPGPU/协处理器的片上内存当中。

Tips:Silvermont一为凌动处理器引入乱序架构的先驱

此前的凌动处理器一直采用顺序执行架构,这在一定程度上是为了降低功耗,但确实对性能有影响。因此在其代号为“BayTrail”的新一代凌动处理器上(主要用于平板电脑、手机、轻薄台式机等低功耗平台),它采用了首次引入乱序执行流水线的Silvermont架构。英特尔宣称Silvermont相比前代Saltwell凌动处理器单线程性能提高了1倍,其实际性能大约为台式机Core微架构的一半。

Tips:Silvermont将大幅提升能效比

选择Silvermont还有着值得玩味的一点:如同我们在2013年15期《英特尔XeonPhi的x86微异构技术解析》一文中分析的,众核处理器的基础核心需要具备高能效,不允许像Haswell那样激进地追求单线程性能。Silvermont核心虽然不比Haswell,但也是一个乱序双发射架构,它能被选中成为众核的基础核心,表明英特尔对Silvermont在14nm上的能效很有自信。